SATRI ICについて

弊社が開発したSATRI回路は、そのユニークな動作原理により多くのオーディオファンの支持を得てきました。

ただ、従来の回路に比べると使用するトランジスタの数が多く、製造コストがかさむという欠点もありました。

そこで弊社においてSATRI回路のIC化を行いました。

もともとSATRI回路はモノリシックIC化を考えて設計しましたので、IC化により理想的な動作をすることになります。

今回のIC化はモノリシックの前段階としてハイブリッドICとしました。

SATRI ICの特徴として次のようなことがあげられます。

・ディスクリートに比べて実装面積が1/4以下になった。

・安定度が大きく向上した。

・非反転出力と反転出力の2つのモードを選べる。

・入力抵抗Rと負荷抵抗RLの2本の抵抗でゲインを決定することができる。

・幅広い電源電圧に対応できる。

・電源の変動に因る影響が少ない、電源電圧が変動しても動作が変わらない。

・動作点の変動が少ない。

・オーディオから計測分野まで幅広いアプリケーションに対応できる。

・無帰還で低い歪み率を実現した。

SATRI-ICの歴史

SATRI-ICは1998年に開発されて以来、いくつかのバージョンアップを経てきました。

ここに、SATRI-ICの歴史をご紹介します。 BPM-7110T 最初に開発されたSATRI-ICです。

デュアルトランジスタチップを使用し、チップ抵抗にはカーボン抵抗を使っていました。

BPM-7110S デュアルトランジスタチップに低雑音のオーディオ用トランジスタを使い、さらに低雑音を目指しました。

BPM-7110HS チップ抵抗に0.1%精度の金属皮膜抵抗を使い、モールドには、新しい1液型エポキシ樹脂を使い、安定度の向上と更なる低雑音を目指しました。

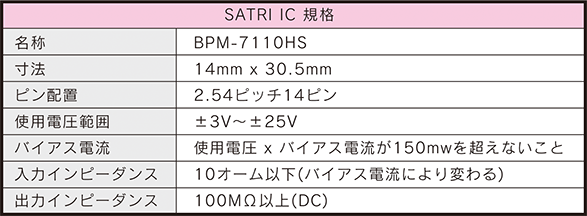

SATRI ICの規格

SATRI ICの規格は次のとおりです。

※仕様電源電圧と、バイアス電流について

SATRI-IC、BPM-7110HSに使用しているトランジスタの定格は、Vcmax50V、Pcmax150mWです。

ですから、この値を超えなければ、トランジスタを破壊する事はありませんが、実装密度が高いので、80%以下を目安にお使いください。例えば、±15Vで使うときは、電源電圧は30Vになりますので、5mAが最大流せる電流ですが、その80%、4mA以下のバイアス電流で使う事をお勧めします。

SATRI ICの使い方

SATRI回路と一般の増幅器の大きな違いは、SATRI回路では入力された信号電流をそのまま出力電流にするだけの働きしかありません。つまり、SATRI回路内部での増幅はないのです。

一般的な増幅器では入力インピーダンスが高く、出力インピーダンスが低くなっています。

これは、電圧信号を扱うのに都合がいいからです。それに対して、SATRI回路の入力インピーダンスはほとんど0で、出力インピーダンスは100Mオーム以上です。

つまり、一般の増幅器とは反対になっています。これは、SATRI回路では、信号は電圧ではなく、電流として扱うからです。

図1でSATRI回路の動作原理を説明します。電圧信号Esは抵抗RによってIsに変換されます。

SATRI回路の入力インピーダンスは0に近いですから、正確に電流に変換されます。

その電流IsはSATRI回路の出力からRLに流し込まれます。SATRI回路の出力は100MΩ以上の高インピーダンスですから、IsはRLを正確に流れます。すると、RLの両端にはオームの法則により、

Eout=Is・RL

の電圧が発生します。

IsにIs=Es/Rを代入すると、

Eout=Es/R・RL

となり、この時の増幅度Aは、

A=RL/R

となります。増幅には抵抗しか関与しないという非常にシンプルな回路です。 一般の増幅器での増幅度Aは、

A=gm・RL

で表されますが、gmは元々非直線性を有しています。そこで出力に歪みを発生するのですが、それを補正するために、負帰還をかけてしのいできました。しかし、負帰還をかけたことで、新たな過渡歪みや時間歪みを発生させてしまいます。

これに対してSATRI回路では増幅に関してはRとRLの単純な抵抗しか関与していませんから、原理的に歪みを発生する要素はありません。ただ、現実問題としては、PNPとNPNトランジスタの特性の違いによるひずみの発生や、オフセットが完全に0にならないことなどの問題がありますが、モノリシック化により、トランジスタのトリミングなどの方法で解決することができると思います。また、一般の増幅器では増幅度をコントロールすることができませんから、出力をコントロールするには2図Aのように、入力側にボリュームを入れて、入力信号のレベルをコントロールするしかありません。

ですから、常に出力にはアンプのノイズがそのまま出力されていますから、-120dBのS/N比を持つアンプでも、ボリュームを40dB絞ったら-80dBのS/Nになってしまいます。これでは、126dBのダイナミックレンジを持ったCDの再生には大きな問題となります。

SATRI回路では図2Bのように、RLをボリュームにすることにより、自由にアンプの増幅度を変えることができます。ですから、ボリュームを絞ればそれだけ増幅度が下がり、同時にノイズもそれに連れて下がっていきます。ですから、SATRI回路でのS/N比はボリュームの位置に関わらず一定です。

図2

上の図は、AMP-5511のVRの位置と雑音電圧、S/N比のデータです。

同じ内部雑音を持ったアンプの入力側にVRをつけた場合のS/Nを茶色のカーブ、SATRI回路のゲイン可変によるデータを赤のカーブで示します。ブルーのカーブはSATRI回路のVR位置による雑音電圧です。これを見ると、通常の入力側にVRを置いた場合は、VRを絞るにつれて、S/Nが悪くなっていきますが、SATRI回路を使ったAMP-5511では、VRを絞るにしたがって雑音電圧は低くなり、S/Nの変化も少なく、VR1の位置でも-83dbを示しています。

また、S/Nに関して、さらに大きな特徴をSATRI回路は持っています。図2Aにおいて、S/Nを大きくするには従来の増幅器ではN、つまりノイズを小さくすることしかできませんでした。そのためにはローノイズの部品を選別したり、動作点をノイズの少ないところを選んだりと、複雑で難しい問題を解決しなければなりませんでした。しかも、原因が熱にある熱擾乱雑音以下にノイズを下げるには、増幅器自体を液体窒素などで冷却するなどの煩雑な方法を取らざるを得ませんでした。

SATRI回路では簡単にS/Nを向上させることができます。SATRI回路ではS/NのS、シグナルを好きなだけ大きくすることができるのです。SATRI回路のSは電流です。電流を大きくするには、単にRを小さくすることで可能となります。SATRI回路のノイズは主にRLの値で決まってきますから、同じ増幅度でS/Nを向上させるには、RとRLの比を一定に保ちながら、その値を下げて行けばいいのです。しかし、いくら大きくできるといっても、使用しているトランジスタのICmaxに制限を受けます。ICmax以上の電流を流すと、トランジスタが破壊されてしまうからです。

ただし、この特徴は今までの増幅器の大きな問題であった、スルーレートの問題を解決しました。SATRI回路では電流の制限を受けませんので立ち上がり時間の制限も受けません。一般の増幅器では入力信号の周波数を上げて行くと、正弦波から三角波になって行きます。これは、電流によって立ち上がり時間の制限を受けるからです。これをスルーレートといいますが、SATRI回路ではその制限がないので周波数を上げていっても出力される信号は正弦波のままです。

このようにSATRI回路では従来の増幅器の問題点をクリアーしています。SATRI回路は従来の増幅回路の延長線上にある回路ではなく、まったく新しい回路です。

ここでSATR ICの基本特性を見てみましょう。OPAMPでは基本特性としてオープンループ特性があります。負帰還をかけないときの増幅度の周波数特性です。それから負帰還をかけたときの特性が推測できます。SATRI回路ではそれに相当するのが出力インピーダンス特性です。それを図3に示します。

図3

10Hz〜10MHzの特性を示します。0dBは231Mオームです。グラフ上の5本の横線はRLの値です。

SATRI回路での出力インピーダンスはRLの値になります。

ですから、この5本の直線はそれぞれのRLの値にしたときの周波数特性を表します。

つまり、周波数特性は、増幅度ではなくRLの値によって決定します。

高周波回路やビデオ回路で使う75オームや50オームでは数10MHzの帯域を実現します。

また、インピーダンスをマッチングさせたいときは、単にRLを使用するインピーダンスの値にすれば良いだけです。

このようにSATRI ICを使うのに難しい計算は必要ありません。必要な帯域のRLを選定し、必要な増幅度を実現するRを選ぶだけでいいのです。

周波数帯域を変化させずに増幅度を変化させるにはRを変化させます。この場合、RLの可変では、RLを0にして増幅度を0にすることができましたが、Rを変化させる場合、増幅度を0にするにはRを無限大にしなくてはならないので、ボリュームとして利用するのには適当ではありませんがゲインのトリムにはうってつけです。次にその様子を見てみましょう。

図4

図4はR=1Kオーム、RL=10Kオーム、ゲイン20dBのときの周波数特性です。

図5

図5は、RLをそのままにし、Rを500オームにしてゲインを26dBにしてみましたが周波数特性は変化しません。

このようにRを変化してゲインを変化させても周波数特性は変化することはありません。

では、入力インピーダンスはどうなっているでしょうか。

図6

図6はSATRI ICの入力インピーダンスです。このように入力インピーダンスは10MHzまで変化はありません。

理想の入力インピーダンスは0ですが、トランジスタの内部抵抗の影響で、数オームの値を持っています。

ですから、入力抵抗Rをそれに近い値で使うときは影響してきます。

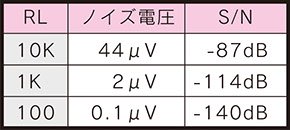

次にSATRI ICのノイズの実測値を挙げます。

実測値はいずれもAカーブを使用しています。面白いのはRLを1/10にするとノイズは、ほぼ1/20になっていることです。

ノイズはRLに比例すると思っていたのですが、ちょっと違うようです。

もっと詳しいデータを取ってみる必要があると思いますが、低雑音にするにはなるべく低いRLを使用することが大変有利になることがこれでわかります。

では、SATRI回路の特性を見てみましょう。まず、群遅延時間です。

図7A

図7B

図7Aは、RL=1Kオーム、R=100オーム、増幅度が10の時の群遅延時間です。

その時の群遅延時間は27.7nSと非常に短い時間です。また、図7BはRL=10Kオーム、R=1Kオーム、増幅度が10の時のもので、約240nSです。

このように、RLが大きくなると群遅延時間も大きくなります。

では、一般の増幅器ではどうでしょうか。

図8

図8は、741タイプのオペアンプに増幅度が10になるようにR1=1Kオーム、RNF=9Kオームで負帰還をかけたものです。

群遅延時間は1.4μSと桁違いに大きいのがわかります。この遅れは大きな過渡歪みを発生します。

このようにSATRI回路は非常に早い応答が特徴です。しかも無帰還ですから過渡歪みの発生はありません。

ここでSATRI回路の特徴をまとめてみます。

・増幅度は外部に接続された2本の抵抗RとRLで決まり、増幅度はRL/Rである。

・入力インピーダンスはR、出力インピーダンスはRLになる。

・周波数特性は出力インピーダンス特性とRLで決まる。

・RLが一定であれば、Rを変化させても周波数特性は変化しない。

・群遅延時間はRLで決定する。RLが小さいほど遅延時間は短くなる。

・ノイズはRLに比例する。ノイズを下げたいときはRLを低くして、Rを下げてS/NのSを大きくする。

・RLをボリュームにすることにより、増幅度を連続的に可変できる。

・スルーレートは電流の制限がないので存在しない。

・過渡歪みの発生がない。

SATRI-ICの構造

SATRI ICの構造は図9のようになっています。

図9

PIN8とPIN12には+、PIN5とPIN1には-の電源バスが入っています。電源が±20VまではOS-CONでバイパス してください。

それ以上の電圧の電源を使うときは、なるべくインピーダンスの低いコンデンサを使ってください。

これは、電源電圧の変動によるバイアス電流の変動を完全に押さえるためです。

PIN11とPIN2は、バイアス電流を設定する端子です。この設定には定電流ダイオード、FETなどの定電流素子を使います。

抵抗でもいいのですが、抵抗の場合、電源電圧の変動によりバイアス電流の変動を受けますので、なるべく定電流素子の使用をお勧めします。その時、この両端の電圧は次の式であらわされます。

・Vb = 2・Vcc-2.4-0.2・Ib

・Vb = バイアス端子両端の電圧

・Vcc=電源電圧の絶対値(±15Vのときは15)

・Ib = バイアス電流(mA)

バイアス電流は、一般のアプリケーション回路なら1〜2mAで良いです。また、電源電圧が高いときや、バイアス電 流を大きく設定する場合は、SATRI ICの最大定格、及びバイアス素子の最大定格内で使うようにしてください。

たとえば定電流素子の定格電力がオーバーする場合は、直列に抵抗を入れると定電流素子にかかる電圧が下がり、定電流素子で消費する電力を下げることができます。

このバイアス電流は、入力回路にバイアスされます。入力回路は入力端子とGND端子があり、そこに電流信号を入力します。

この場合、電圧信号を入れても正常に動作しません。必ず、入力抵抗Rで電流に変換するか、電流源を接続してください。

入力回路の出力はバイアス電流と信号電流が加算された電流になります。この電流は電流反転回路に入力されます。

出力には、入力電流が反転されて出力されます。電流反転回路の+と-の出力を接続し、GNDとの間に負荷抵抗RLを接続すると、RLには信号電流だけが流れ、出力電圧Eout=信号電流・RLが得られます。

RLをボリュームにすると連続的に増幅度を変化することができます。

この時、入力電圧と出力電圧は位相が逆になります。

SATRI ICには入力と出力の位相を同じにするために、もう一つの電流反転回路が入っています。

正相の出力を得るためには、一段目の電流反転出力+と2段目の電流反転入力-、電流反転出力-と2段目の電流反転入力+を接続し、2段目の電流反転出力の+と-を接続し、そこにRLをGNDの間に入れることで実現できます。

図10

実際のSATRI ICのピン配置は図10のとおりです。

・Pin1、Pin5:-Vcc1,2、マイナス電源です。

二つのPinは内部で接続されています。なるべく近い位置でOS-CONなどの良質のコンデンサでバイパスしてください。

ここの変動を低く抑える事がSATRI-ICを確実に動作させるためには必要です。

・Pin2、Pin11:CS-+、バイアス電流の設定端子です。

バイアス電流はPin11のCS+から、CS-に向かって流れるようにします。

詳しい設定方法は、「アプリケーション設計ガイド」をお読みください。

・Pin3、Pin10:Nout-+、反転出力端子です。

ここからの出力は電圧出力ではなく、電流出力である事にご注意ください。

通常はPin3とPin10を接続し、GNDとの間に負荷抵抗RLを接続する事によって、電流を電圧に変換する事が出来ます。

・Pin4、Pin9:Pin-+、電流反転回路への入力です。

正相出力が必要なときは、Pin3とPin9、Pin10とPin4を接続します。

・Pin6、Pin7:Pout-+、正相出力端子です。

Pin6とPin7を接続し、GNDとの間に負荷抵抗RLを接続すると、正相電圧出力が得られます。

・Pin8、Pin12:+Vcc1,2、プラス電源です。

二つのPinは、内部で接続されています。なるべく近い位置でOS-CONなどの良質のコンデンサでバイパスしてください。

ここの変動を低く抑える事がSATRI-ICを確実に動作させるためには必要です。

・Pin13:GNDです。

確実にGNDと接続してください。

・Pin14:信号電流入力です。

電圧信号を入力すると、ICを破壊する恐れがありますので、必ず抵抗で電流に変換してから入力してください。

ピンの間隔は、2.54mmピッチを基本にしていますから、2.54mmピッチのユニバーサル基板を使って簡単にアプリケーションを組むことができます。

SATRI-ICによる応用回路

SATRI ICを使った応用回路を説明します。

図11

基本的な非反転回路を図11に示します。

この回路では、入力される信号電圧と同相の出力信号電圧が得られます。また、回路の増幅度はRL/Rです。

増幅度はデータにあったように、わずかに理論値より少なくなりますから、厳密な増幅度の設定が必要なときはRをトリミングするといいでしょう。

次に反転回路を示します。

図12

反転回路では、単に2段目の電流反転回路を使わないようにすれば実現できます。

また両回路とも、バイアス電流の設定には定電流ダイオード(CRD)を使っていますが、FETを使うこともできます。

この時の回路に流れる電流は、無信号時、反転回路のときはバイアス電流の4倍、非反転回路のときはバイアス電流の5倍の電流が流れます。

非反転回路、反転回路を並列にすると、BTL回路が構成されます。その時の入力インピーダンスはRの半分の値になることに注意してください。基本回路では入力インピーダンスはR、出力インピーダンスはRLになるので、入力インピーダンスを高くしたい場合や、出力インピーダンスを低くしたい場合など制限が出てきます。

そこで、一般的な回路としては、図13のようにSATRI ICの前後にインピーダンス変換のためのバッファを挿入します。

図13

このような構成にすると、RとRLの選択の自由度が大きくなりますので、目的に合った増幅器を構成することが容易です。

ただ、入力側のバッファのノイズはRとRLにより増幅されますから、雑音の少ない回路を選ぶことが必要です。

また、出力側のバッファは、RLをボリュームにしたとき、0に絞り込んだときでも雑音は残ることになります。

しかし、普通は数マイクロボルトオーダーですから問題になりません。

ではこの回路の応用としてパワーアンプを構成してみましょう。

図14はSATRI ICを使ったパワーアンプです。このアンプは大きく分けて4つの部分で構成されています。

1. TR1、2、3、4で構成される入力バッファ

2. SATRI ICとRとRLで構成されるSATRI回路

3. TR5、6、7、8、9、10、11、12で構成される出力バッファ

4. OPAMPで構成されるDCサーボ

入力バッファはダイヤモンド回路で構成されています。TR1、2とTR3、4は小信号のコンプリメンタリを使います。

同じトランジスタで構成すると、入力側出力側には同じバイアス電流が流れます。

ただ、入力抵抗はあまり大きく取れませんので、入力抵抗を大きくしたいときはFETを使ったバッファを使います。

また、最大入力信号は1V位を想定していますので、その電圧でRを歪みなく駆動できるか確認が必要です。

SATRI回路はバイアス電流を1.5mAのCRDで設定してあります。ここはFETを使ってもいいと思います。

RLは10KのAカーブのボリュームを使います。RLはなるべく小さくしたいところですが、10Kオーム以下のAカーブのボリュームは手に入りにくいので10Kオームを選びました。

出力バッファはダーリントン接続のダイヤモンド回路です。

TR5、6は小信号のコンプリメンタリ、TR7、8、9、10は中信号のコンプリメンタリ、TR11、12は電力用の30〜50Wのコンプリメンタリを選ぶといいでしょう。VR1、2はバイアス電流設定用です。

電源電圧を±16V位にすると8オームで10W程度の出力が得られます。

DCサーボ回路はオフセットとドリフトを押さえるためにつけます。SATRI ICはドリフトは小さいのですが、PNPとNPNの特性の違いによるオフセットは無視できません。

打ち消し回路をつけてもいいのですが、電源電圧の変動の影響を受けないようにするには結構複雑な回路になります。

そこで、DCサーボ回路を採用します。ただ、SATRI回路でRLをボリュームとしたためゲインが変化しますので、そのときDCのレベルが動かないようにフィルターは過制動の設定にしてあります。

調整は、VR1、2を0にしておき、RLを0にします。この状態で電源を入れ、バイアス電流が100mA程度にします。

その時の出力DCが0Vになるように調整します。

これは、RLを0にしたときはゲインが0になりますので、DCサーボが働かなくなるからです。

調整が終われば、ボリュームを動かしても出力のDCは動かないはずです。

すべてのバイバスコンデンサはOS-CONを使うようにしましょう。

OS-CONの広帯域のインピーダンスの低さは、SATRI回路の色づけのない音色には不可欠なアイテムです。

電源はなるべく定電圧電源にしてください。安定化することで、バッファ回路のバイアスの変動もなくなり、アンプの動作が精密になります。これにより、SATRI ICを使ったアンプはすべての情報を超精密に描写します。

安定化電源はフィードバックタイプは使わないでください。図15にその例を示します。

図15Aは2個のCRDを使っています。

この回路では簡単ですが、CRDのばらつきによるアンバランス分はGNDに流れてしまいます。

図15Bはこれを改良したもので、カレントミラー回路を使って1個のCRDで済ませています。

この回路では定電圧ダイオードに流れる電流は同じですから、アンバランスが発生することはありません。

CRDに比べるとTRは安いですからこちらの回路をお勧めします。

また、デュアルトランジスタが手に入らないときは2個のトランジスタを熱結合して使ってください。

また、定電圧ダイオードは必ず低雑音タイプを使ってください。入力側の電圧は25V位でいいと思います。

ただOS-CONでは手に入りやすいものは25V耐圧までですから35V耐圧の電解コンデンサを使います。

OS-CONの連続使用電圧は耐圧の80%ですから、これは必ず守りましょう。

SATRI ICのオフセットの打ち消しは図14に示したようにOPAMPによるDCサーボが最適です。

ドリフトはRLをむやみに大きくしない限り安定しています。

また、SATRI回路自体無帰還ですのでサーボも安定してかかります。

ただし、RLにボリュームを使う場合は0に絞りきった場合サーボループが切れますからDCサーボがかかりません。

ですから、出力側のバッファのオフセット調整は必要です。

SATRI ICの出力にバイアス素子を入れる方法も有効ですが、その場合、RLのボリュームを絞りきった場合、バイアス素子の内部抵抗がRLとなって完全には絞り切ることができません。

RLをボリュームにする場合は、図14のような出力側のバッファのバイアスが独立した回路の方が良いです。